Analogix Continues To Innovate In High-Speed Low-Power Signal Conditioning Technology To Bring New Features To The Market

Below is our recent interview with Miguel Rodriguez, Director of Product Marketing at Analogix:

Q: Can you tell us something more about the company and what you do?

A: Analogix is the market leader in providing end-to-end interface connectivity semiconductor solutions for DisplayPort™ under the SlimPort® brand and for USB™, such as high-speed signal conditioners (retimers). Our SlimPort® high-speed, low-power retimers push higher data throughput over long distances for notebooks, 2-in-1 convertibles, desktop PCs, and smartphones.

Q: Earlier this year you’ve announced the availability of your second generation ANX74xx family of 10 Gbps USB-C™ retimers. Why is now the time for such a solution?

A: USB 3.2 is a boost in data transfer bandwidth up to 10 Gbps. The new SuperSpeed USB specification in Generation 2 of USB 3.2 delivers improved data encoding and efficiency, doubling the speed of the Generation 1 standard (5Gbps).

USB Type-C™, also known as USB-C, supports the latest USB 3.2 standard. Full-Featured USB Type-C™ cables can support up to 10Gbps of data throughput, following the USB3.2 Gen2 standard, as well as up to 8.1Gbps per lane and up to 4-lanes of display throughput, following the DisplayPort v1.4 standard. Transmitting high-speed data over a cable or printed-circuit-board (PCB) path significantly attenuates and distorts the signal and the solution to that is the retimer.

Retimers filter out the incoming jitter while remaining compliant to the specifications of the serial interface for all functional purposes. They support multiple industry standards: Universal Serial Bus 3.2 specification, USB Type-C™ specification, VESA DisplayPort™ 1.4a, and DisplayPort™ over USB-C™. Analogix’s second generation ANX74xx retimer family brings improved performance to the market-proven ANX74xx re-timer product architecture, previously adopted by the Intel Comet Lake platform.

Q: What makes it the top re-timer solution for next generation Intel notebooks and desktop PCs?

A: The Analogix retimer technology is the first to fully support the USB Specification for repeaters. The USB specification is very clear on the requirements for retimers. Analogix is the first vendor with industry proven architecture which meets and exceeds the USB specification for both 5Gbps (BLR) and 10Gbps (SRIS) retimers.

Built on industry proven architecture previously adopted by Intel, AMD, and Nvidia CPU/GPU platforms, the second generation ANX74xx family features an even lower power consumption, integrated clock source, and improved robustness of DisplayPort 1.4a and USB 3.2., offering:

– Loss compensation to recover up to 23dB channel loss for USB 3.2 Gen 2 10 Gbps, and up to 27dB for DisplayPort;

– Support for full DisplayPort retimer function with Link Training Tunable PHY Repeater (LTTPR) in transparent and non-transparent mode with AUX snooper, guaranteeing a loss compensation to recover up to 27dB channel loss for DisplayPort HBR3 8.1Gbps;

– Full compliance to the latest USB 3.2 specification with added emphasis on the re-timer requirements defined in Appendix E, which specifies support for 4-re-timer connectivity with seamless cascading of four re-timers, meeting the USB 3.2 CTS requirements.

Q: How is Analogix’s retimer architecture different from other vendors?

A: The Analogix architecture is in its second generation and has been industry-proven since the introduction of its first generation in 2017. The Analogix retimer architecture is fully compliant to the SRIS architecture for 10Gbps USB data transfers and BLR for 5Gbps data transfers, both which are required and defined in the USB specification. Other competing technologies in the market only support BLR architecture for 5Gbps function and thus violating the specification for 10Gbps data transfers.

The re-timer architecture and design will dictate whether compliance is achieved at Gen 1 (5G) only or Gen 1 and Gen 2 (5G and 10G respectively). 10G active re-timer solutions for USB-C also support 5G.

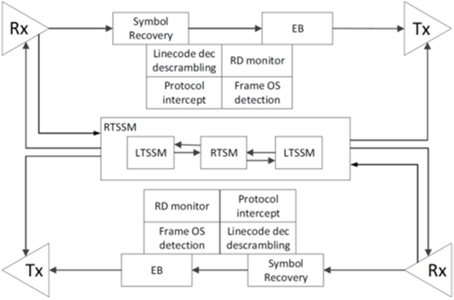

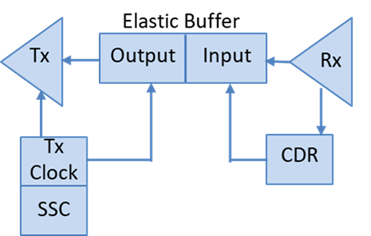

– SRIS (Separate Reference Clock Independent SSC) – it is defined for USB Gen2 operation and it features a physical layer protocol aware and software transparent extension device which creates two separate electrical link segments. It implements an independent reference clock architecture using a local clock as input clock for the transmitter (Tx) and it is completely isolated from the receiver (Rx) clock, including SSC.

Fig. 1

Fig. 2

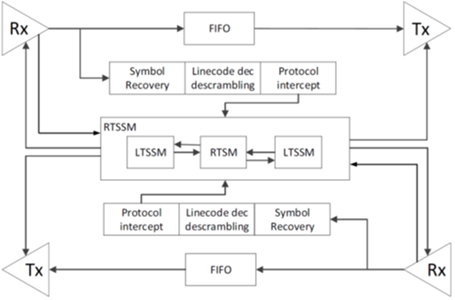

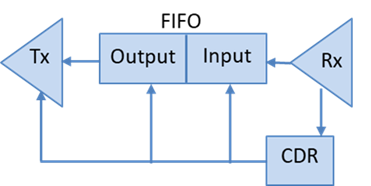

– BLR (Bit-Level Retimer) – it is defined for USB Gen1 operation only and it features a physical layer protocol aware and software transparent extension device which creates two separate electrical link segments. It implements a recovered clock architecture.

Fig. 3

It uses a recovered clock from input data stream as input clock for transmitter (Tx), same as the receiver (Rx) clock.

Fig. 4

The BLR architecture was designed and specified for 5G only, not 10G. The Rx PHY on Hosts and Devices are not designed for Gen2 BLR operation, the BLR clock switching mechanism at 10G is not implemented and not tested. Therefore, jitter transfer characteristics of BLR at Gen2 cannot be guaranteed when cascading multiple re-timers (two or more). The Host will be exposed to Devices that were not designed for, simulated, or tested at 10G, and hence, BLR behavior cannot be predicted.

The SRIS architecture is required for Gen2 10G operation in USB Spec and CTS because the recovered clock in BLR transfers too much jitter.

Q: How hard was it in terms of development process?

A: Retimers are by definition protocol aware. The protocol layer handles link training at each link segment independently.

That is, retimers have a digital state machine aspect associated with them. In order to properly transition in and out of each state, the designer must have intimate knowledge of the USB retimer specification for both 10Gbps and 5 Gbps, excellent analog design for the PHY, as well as in depth USB system knowledge.

Q: What we can look forward to seeing from Analogix Semiconductor next?

A: Analogix will continue to innovate in high-speed low-power signal conditioning technology to bring new features to the table. The next generation of USB, called USB4, provides a large advantage over USB 3.x in that not only does it doubles the data rate of USB3.x (per lane) but also improves the transmit protocol to allow the encapsulation of other protocols.